PCS/PMA Configuration#

This section only applies to ports on high speed modules, supporting rates at 40G or higher. For ports on these modules, an additional sub-tab PCS/PMA Config & Status will appear in the main Resource Properties tab.

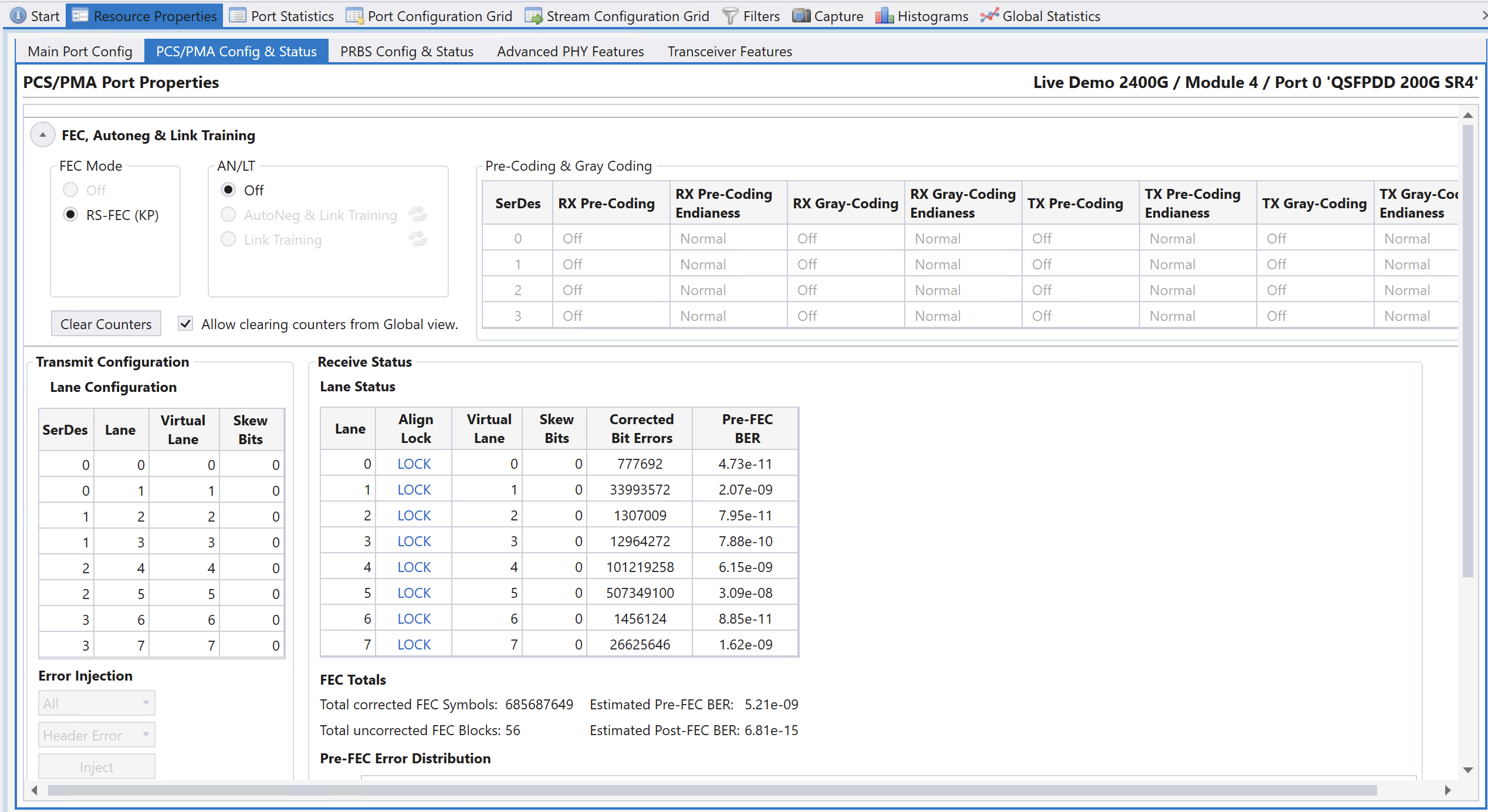

Fig. 62 PCS/PMA Config & Status#

At the top of the page you can Enable Forward Error Correction (FEC) if that is supported by the port - for PAM4 ports, RS-FEC is always enabled.

Note

Port speeds of 10G/25G on Loki support Firecode FEC

You can also Enable Link Training and Enable Autoneg (Autonegotiation) if that is supported by the port.

Please observe that if you Enable Autoneg, Link Training will also be enabled and conducted after the Autonegotiation.

Clear Counters will clear the counters on the page and by checking Allow clearing counters from Global view you can use the clear counters facilities in the Global Statistics pages to clear the counters in this page.

What is shown on the rest of this page depends on the configuration of the selected port.

PAM4 Ports#

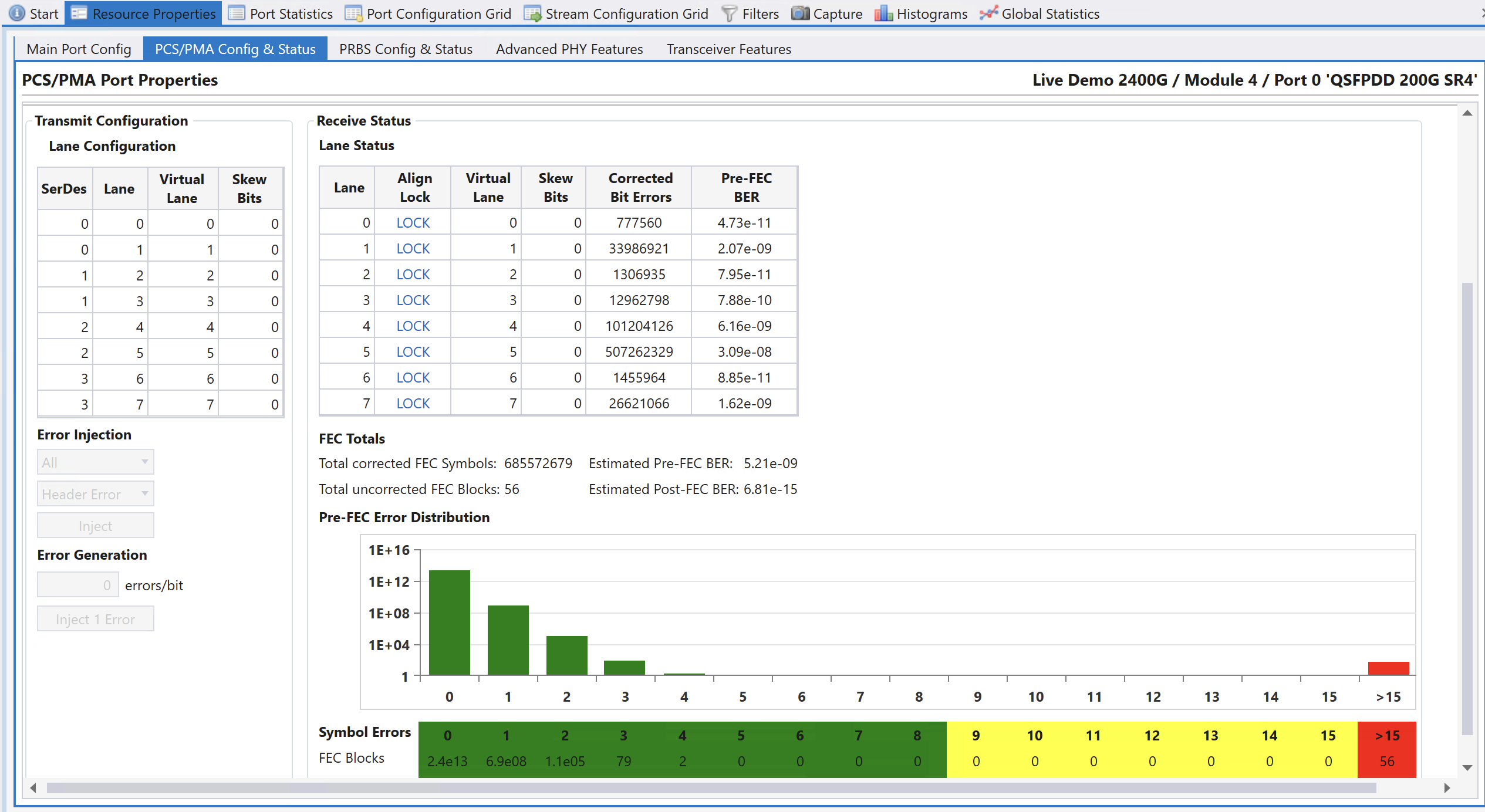

The image below shows what you can see on a PAM4 port, in this case a 400G port:

Fig. 63 PCS/PMA Config & Status (PAM4 Ports)#

In the Transmit Configuration section you can for each physical Lane on the port see the SerDes, and Lane. You can change the Virtual Lane used for the physical lane and set Skew Bits for each lane.

In the Receive Status section you can for each physical Lane see if it is in Align Lock (Alignment lock), the Virtual Lane used for the physical lane and set Skew Bits for each lane. In addition, you for each lane can see number of Corrected Bit Errors and the estimated Pre-FEC BER.

The lower part of the page contains FEC statistics for the port:

Total corrected FEC Symbols

Total uncorrected FEC blocks

Estimated Pre-FEC BER

Estimated Post-FEC BER

You will also find the Pre-FEC Error Distribution graph. Here you can see number of received FEC blocks with 0, 1, 2.. up to 15 symbol errors. This is what the RS-FEC used for PAM4 signals will correct. You can also see number of received FEC blocks with more than 15 symbol errors. This is more than the RS-FEC used for PAM4 signals can correct so this will cause uncorrected FEC blocks to be counted and most likely also cause errors at higher layers in the received signal.

Note

Error injection is currently not implemented.

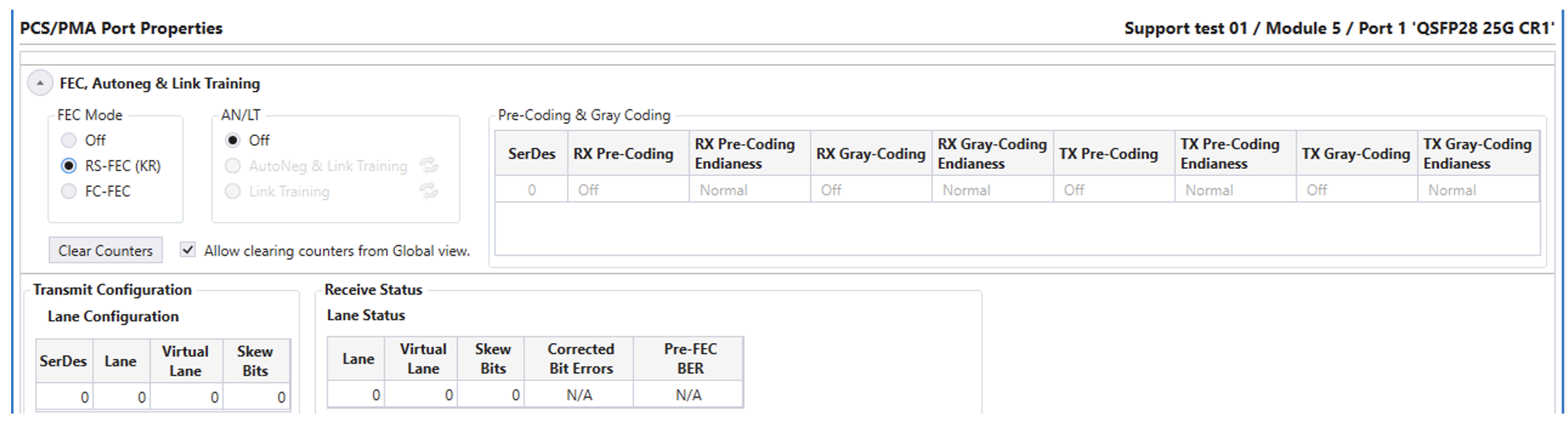

NRZ Ports With FEC#

The image below shows what you can see on a NRZ port with FEC, in this case a 100G port.

Fig. 64 PCS/PMA Config & Status (NRZ Ports w/ FEC)#

Most is similar to what you can control and see for PAM4 ports. Please also observe that the RS-FEC used for NRZ signals will correct up to 7 symbol errors. The Pre-FEC Error Distribution graph is adjusted accordingly.

Some ports also support Firecode FEC when running at 10G and 25G NRZ.

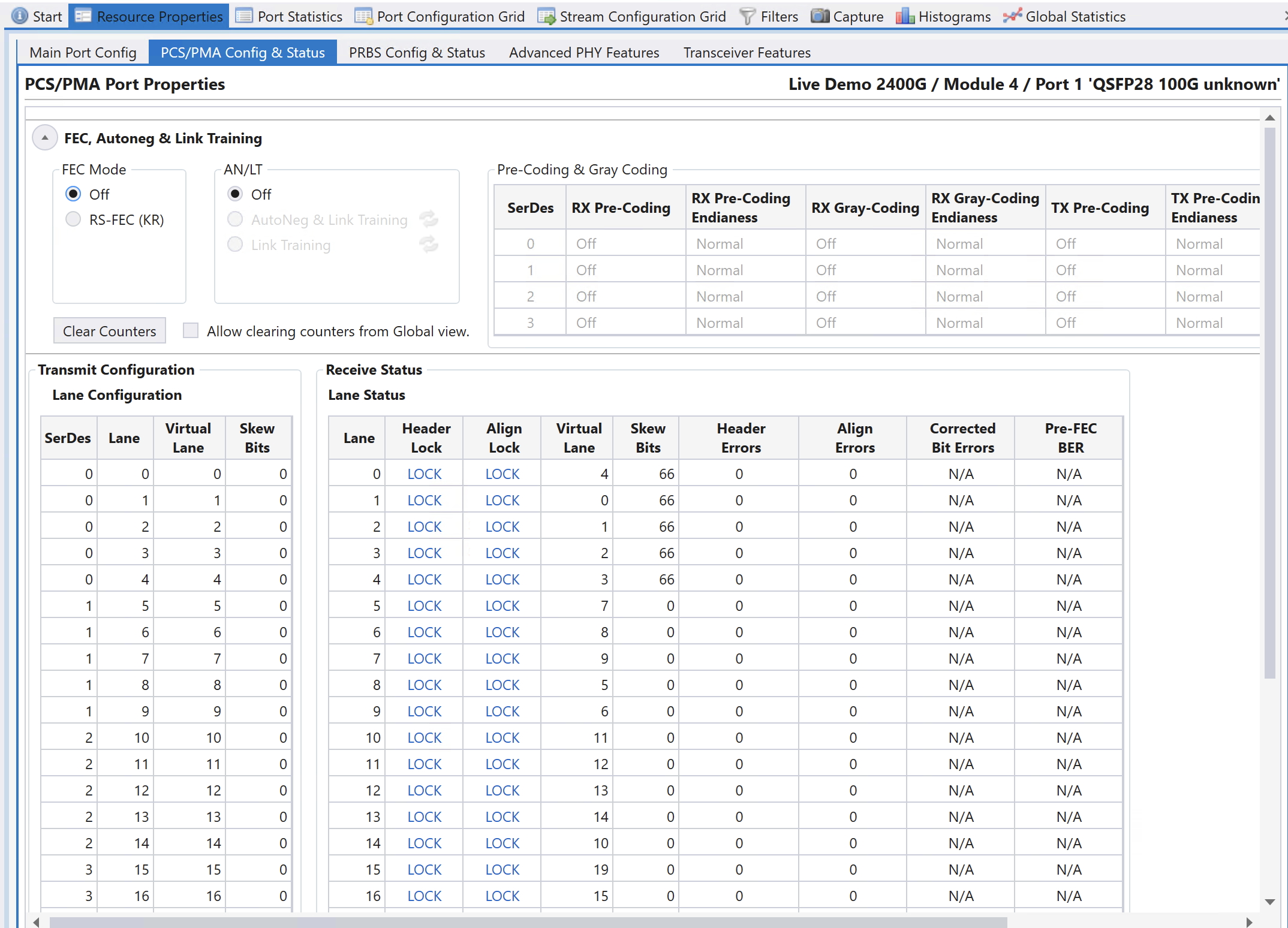

NRZ Ports Without FEC#

The image below shows what you can see on a NRZ port without FEC, in this case a 100G port.

Fig. 65 PCS/PMA Config & Status (NRZ Ports w/o FEC)#

Most is similar to what you can control and see for PAM4 ports in the Transmit Configuration and Receive Status tables. Please observe however that in the Receive Status table you can see additional counters for Header Errors, Alignment Errors. The Corrected Bit Errors and the Pre-FEC BER counters are not updated for ports without RS-FEC.