PRBS

Pseudo Random Binary Sequence (PRBS) is a technique used for testing and evaluating the performance of Ethernet interfaces, particularly those operating at high speeds. PRBS is a type of test pattern used to generate a known, repetitive, and pseudorandom sequence of binary (0s and 1s) data.

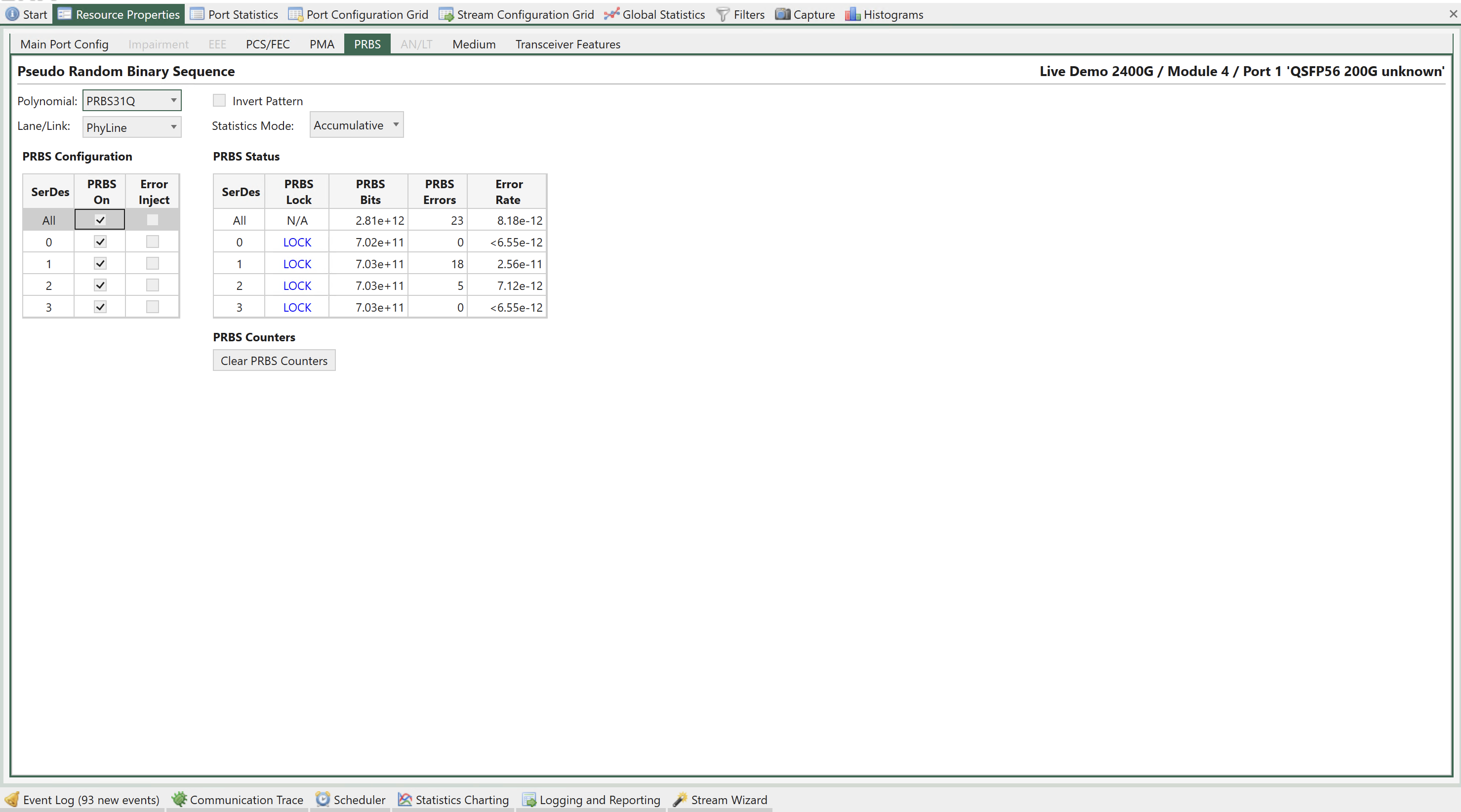

Fig. 104 Port Properties - PRBS

All ports supporting Layer 1 PRBS testing will support the Polynomial PRBS31. If more are supported they can be selected from the drop down menu you get when you click on the selection box. Some ports supporting Layer 1 PRBS testing will support Invert Pattern. Check the box to invert the test pattern if supported by the port. With Statistics mode Accumulative, PRBS Status Counters are accumulated since last time Clear PRBS Counters was pressed. With Last Second PRBS Status Counters are shown for the last second. Lane/Link is for future use.

PRBS Configuration

The physical lanes of ports supporting Layer 1 PRBS testing can be set to PRBS mode, where they transmit a PRBS bit pattern, which can be useful for testing physical cabling and connectors.

On the transmit side, you select whether each lane should be in PRBS mode, and also whether it should be subject to error injection:

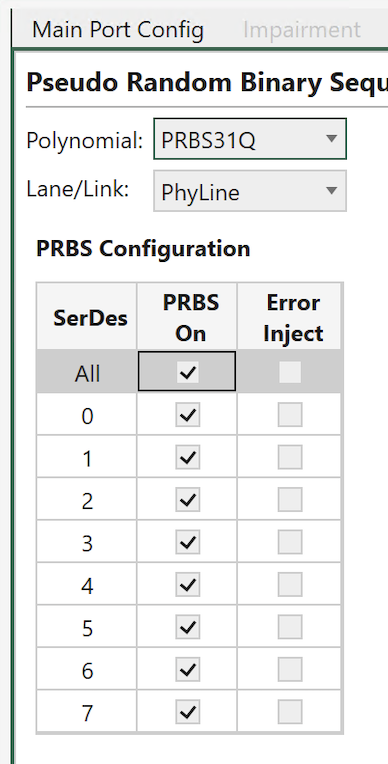

Fig. 105 Port Properties - PRBS TX configuration

Test Patterns

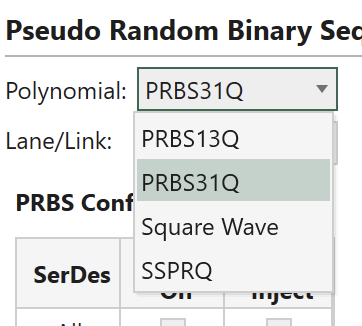

On Z800 Freya 112G serdes, available patterns are:

PRBS13Q (IEEE 802.3 Claus 120.5.11.2.1)

PRBS31Q (IEEE 802.3 Claus 120.5.11.2.2)

SSPRQ (IEEE 802.3 Claus 120.5.11.2.3)

Square Wave (IEEE 802.3 Claus 120.5.11.2.4)

Fig. 106 Test Patters on Z800 Freya

Note

Why SSPRQ?

The PRBS13Q pattern (IEEEE 802.3 Clause 120.5.11.2.1) is conveniently short (8191 symbols), but is much less stressful than long periods of random data. In contrast, the PRBS31Q pattern (IEEEE 802.3 Clause 120.5.11.2.2) is more stressful than long periods of random data. However, its length of 2,147,483,647 symbols makes it challenging for easy capture and analysis.

The SSPRQ pattern, short for Short Stress Pattern Random Quaternary, (IEEEE 802.3 Clause 120.5.11.2.3) strikes a balance, being short enough for capture while being more stressful than extended random data periods. SSPRQ consists of a repeating PAM4 symbol sequence of 2^16-1, derived from 4 sequences incorporating key stressors from PRBS31. Despite its stress-inducing nature, SSPRQ remains manageable for analysis with advanced tools such as Equalization and Jitter/Noise analysis, making it suitable for Optical TX testing purposes.

On Z400 Thor 56G serdes, available patterns are:

PRBS7Q

PRBS9Q

PRBS10Q

PRBS11Q

PRBS13Q

PRBS15Q

PRBS20Q

PRBS23Q

PRBS31Q

PRBS49Q

PRBS58Q

On Z100 Loki 25G serdes, available patterns are:

PRBS31

Error Injection

Errors can be injected individually by clicking a button, or continuously by specifying a rate. Error injection also works for lanes that are not in PRBS mode, and can thus be used to simulate bit-level errors into the CAUI level.

PRBS Status

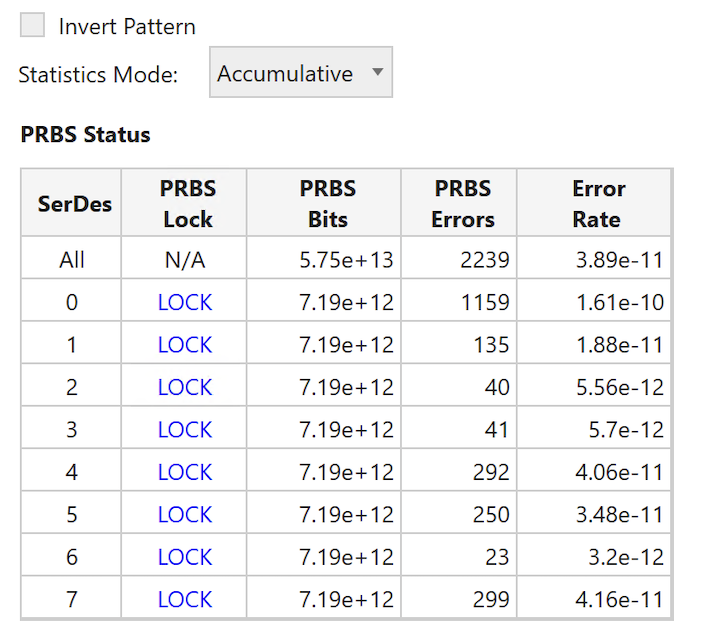

On the receive side, you can see whether each physical lane has locked onto the PRBS pattern, and the number of bit errors while in PRBS lock:

Fig. 107 Port Properties - PRBS RX status